## ADC0820-N 8-Bit High Speed µP Compatible A/D Converter with Track/Hold Function

Check for Samples: ADC0820-N

#### **FEATURES**

- **Built-In Track-and-Hold Function**

- **No Missing Codes**

- No External Clocking

- Single Supply—5 V<sub>DC</sub>

- Easy Interface to All Microprocessors, or **Operates Stand-Alone**

- **Latched TRI-STATE Output**

- Logic Inputs and Outputs Meet Both MOS and T<sup>2</sup>L Voltage Level Specifications

- **Operates Ratiometrically or with any** Reference Value Equal to or Less than V<sub>CC</sub>

- **0V to 5V Analog Input Voltage Range with** Single 5V Supply

- No Zero or Full-Scale Adjust Required

- **Overflow Output Available for Cascading**

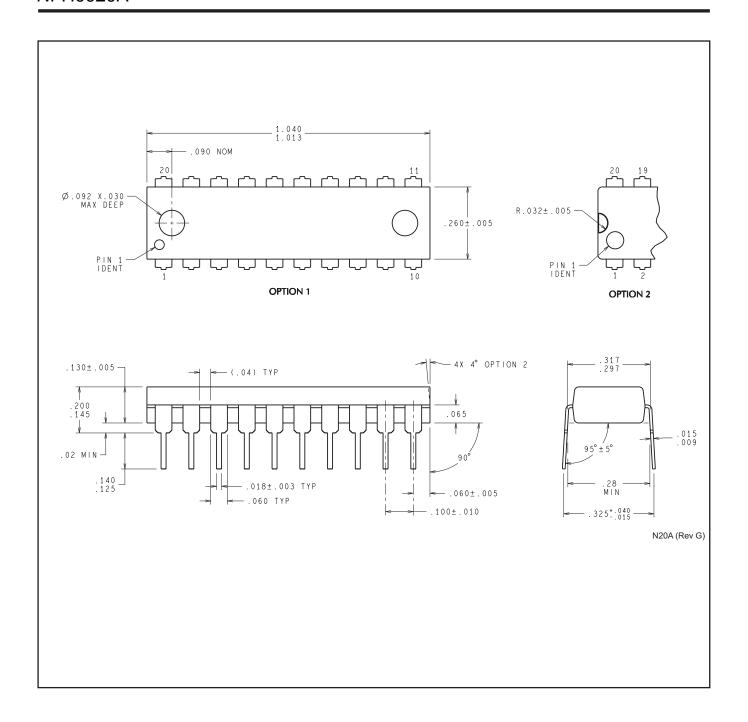

- 0.3 in. Standard Width 20-Pin PDIP

- 20-Pin PLCC

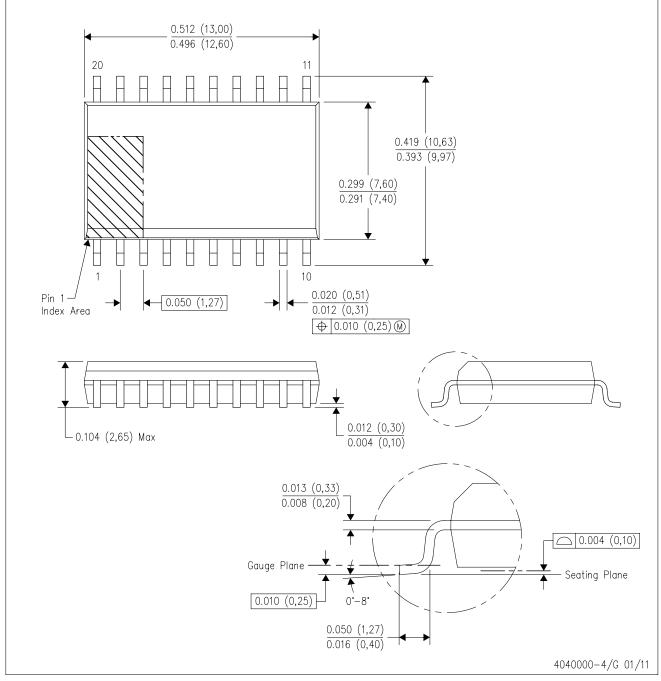

- 20-Pin SOIC

## **KEY SPECIFICATIONS**

- **Resolution: 8 Bits**

- **Conversion Time**

- 2.5 µs Max (RD Mode)

- 1.5 µs Max (WR-RD Mode)

- Low Power: 75 mW Max

- Total Unadjusted Error:  $\pm \frac{1}{2}$  LSB and  $\pm 1$  LSB

#### DESCRIPTION

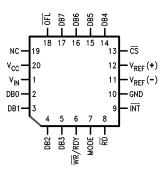

By using a half-flash conversion technique, the 8-bit ADC0820-N CMOS A/D offers a 1.5 µs conversion time and dissipates only 75 mW of power. The halfflash technique consists of 32 comparators, a most significant 4-bit ADC and a least significant 4-bit ADC.

The input to the ADC0820-N is tracked and held by the input sampling circuitry eliminating the need for an external sample-and-hold for signals moving at less than 100 mV/µs.

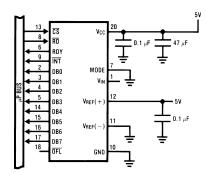

For ease of interface to microprocessors, the ADC0820-N has been designed to appear as a memory location or I/O port without the need for external interfacing logic.

#### **Connection and Functional Diagrams**

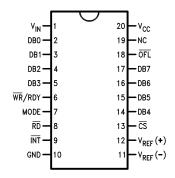

Figure 1. CDIP, PDIP. and SOIC Packages (Top View)

Figure 2. PLCC Package

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Figure 3. Functional Diagram

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **Absolute Maximum Ratings** (1)(2)(3)

|                                              | , •           |                                |                 |  |  |

|----------------------------------------------|---------------|--------------------------------|-----------------|--|--|

| Supply Voltage (V <sub>CC</sub> )            |               | 10V                            |                 |  |  |

| Logic Control Inputs                         |               | -0.2V to V <sub>CC</sub> +0.2V |                 |  |  |

| Voltage at Other Inputs and Output           |               | -0.2V to V <sub>CC</sub> +0.2V |                 |  |  |

| Storage Temperature Range                    |               |                                | −65°C to +150°C |  |  |

| Package Dissipation at T <sub>A</sub> = 25°C |               |                                | 875 mW          |  |  |

| Input Current at Any Pin (4)                 |               |                                | 1 mA            |  |  |

| Package Input Current <sup>(4)</sup>         |               |                                | 4 mA            |  |  |

| ESD Susceptibility <sup>(5)</sup>            |               |                                | 900V            |  |  |

|                                              | PDIP Package  |                                | 260°C           |  |  |

| Load Town (Coldering 10 and)                 | CDIP Package  | CDIP Package                   |                 |  |  |

| Lead Temp. (Soldering, 10 sec.)              | COIC Dealrage | Vapor Phase (60 sec.)          | 215°C           |  |  |

|                                              | SOIC Package  | Infrared (15 sec.)             | 220°C           |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

- (2) All voltages are measured with respect to the GND pin, unless otherwise specified.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supply rails (V<sub>IN</sub> < V<sup>-</sup>or V<sub>IN</sub> > V<sup>+</sup>) the absolute value of current at that pin should be limited to 1 mA or less. The 4 mA package input current limits the number of pins that can exceed the power supply boundaries with a 1 mA current limit to four.

- (5) Human body model, 100 pF discharged through a 1.5 kΩ resistor.

## Operating Ratings<sup>(1)(2)</sup>

| - 1                                                                     |                                                              |                             |

|-------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|

|                                                                         | ADC0820CCJ, ADC0820CIWM                                      | -40°C≤T <sub>A</sub> ≤+85°C |

| Temperature Range (T <sub>MIN</sub> ≤T <sub>A</sub> ≤T <sub>MAX</sub> ) | ADC0820BCN, ADC0820CCN, ADC0820BCV, ADC0820BCWM, ADC0820CCWM | 0°C≤T <sub>A</sub> ≤70°C    |

| V <sub>CC</sub> Range                                                   |                                                              | 4.5V to 8V                  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

- (2) All voltages are measured with respect to the GND pin, unless otherwise specified.

## **Converter Characteristics**

The following specifications apply for RD mode (pin 7 = 0),  $V_{CC} = 5V$ ,  $V_{REF}(+) = 5V$ , and  $V_{REF}(-) = GND$  unless otherwise specified. **Boldface limits apply from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_i = 25^{\circ}C$ .

| Parameter                                  | Conditions                       |                    | ADC0820C                       | CJ                             | ADC082<br>ADC0820<br>ADC0820 | Limit                          |                                |       |

|--------------------------------------------|----------------------------------|--------------------|--------------------------------|--------------------------------|------------------------------|--------------------------------|--------------------------------|-------|

|                                            |                                  | Typ <sup>(1)</sup> | Tested<br>Limit <sup>(2)</sup> | Design<br>Limit <sup>(3)</sup> | Typ <sup>(1)</sup>           | Tested<br>Limit <sup>(2)</sup> | Design<br>Limit <sup>(3)</sup> | Units |

| Resolution                                 |                                  |                    | 8                              |                                |                              | 8                              | 8                              | Bits  |

|                                            | ADC0820BCN, BCWM                 |                    |                                |                                |                              | ±½                             | ±1/2                           | LSB   |

| Total Unadjusted                           | ADC0820CCJ                       |                    | ±1                             |                                |                              |                                |                                | LSB   |

| Error <sup>(4)</sup>                       | ADC0820CCN, CCWM, CIWM           |                    |                                |                                |                              | ±1                             | ±1                             | LSB   |

|                                            | ADC0820CCMSA                     |                    |                                |                                |                              | ±1                             | ±1                             | LSB   |

| Minimum Reference<br>Resistance            |                                  | 2.3                | 1.00                           |                                | 2.3                          | 1.2                            |                                | kΩ    |

| Maximum Reference<br>Resistance            |                                  | 2.3                | 6                              |                                | 2.3                          | 5.3                            | 6                              | kΩ    |

| Maximum V <sub>REF</sub> (+) Input Voltage |                                  |                    | V <sub>CC</sub>                |                                |                              | V <sub>CC</sub>                | V <sub>cc</sub>                | V     |

| Minimum V <sub>REF</sub> (⁻) Input Voltage |                                  |                    | GND                            |                                |                              | GND                            | GND                            | ٧     |

| Minimum V <sub>REF</sub> (+) Input Voltage |                                  |                    | V <sub>REF</sub> (-)           |                                |                              | V <sub>REF</sub> (-)           | V <sub>REF</sub> (-)           | ٧     |

| Maximum V <sub>REF</sub> (-) Input Voltage |                                  |                    | V <sub>REF</sub> (+)           |                                |                              | V <sub>REF</sub> (+)           | V <sub>REF</sub> (+)           | V     |

| Maximum V <sub>IN</sub> Input<br>Voltage   |                                  |                    | V <sub>CC</sub> +0.1           |                                |                              | V <sub>CC</sub> +0.1           | V <sub>CC</sub> +0.1           | V     |

| Minimum V <sub>IN</sub> Input<br>Voltage   |                                  |                    | GND-0.1                        |                                |                              | GND-0.1                        | GND-0.1                        | V     |

| Maximum Analog                             | CS =V <sub>CC</sub>              |                    |                                |                                |                              |                                |                                |       |

| Input Leakage                              | V <sub>IN</sub> =V <sub>CC</sub> |                    | 3                              |                                |                              | 0.3                            | 3                              | μΑ    |

| Current                                    | V <sub>IN</sub> =GND             |                    | -3                             |                                |                              | -0.3                           | -3                             | μΑ    |

| Power Supply<br>Sensitivity                | V <sub>CC</sub> =5V±5%           | ±1/16              | ±1/4                           |                                | ±1/16                        | ±1/4                           | ±1/4                           | LSB   |

Typicals are at 25°C and represent most likely parametric norm. Tested limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

Design limits are specified but not 100% tested. These limits are not used to calculate outgoing quality levels. Total unadjusted error includes offset, full-scale, and linearity errors.

## **DC Electrical Characteristics**

The following specifications apply for  $V_{CC} = 5V$ , unless otherwise specified. **Boldface limits apply from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25$ °C.

| Parameter                                           | Cor                                                          | nditions                                                                 | ,                  | ADC0820CC                      | J                              | ADC0820            | ADC0820BCN, ADC0820CCN,<br>ADC0820BCV, ADC0820BCWM,<br>ADC0820CCWM, ADC0820CIWM |                                |       |  |

|-----------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|--------------------------------|--------------------------------|--------------------|---------------------------------------------------------------------------------|--------------------------------|-------|--|

|                                                     |                                                              |                                                                          | Typ <sup>(1)</sup> | Tested<br>Limit <sup>(2)</sup> | Design<br>Limit <sup>(3)</sup> | Typ <sup>(1)</sup> | Tested<br>Limit <sup>(2)</sup>                                                  | Design<br>Limit <sup>(3)</sup> | Units |  |

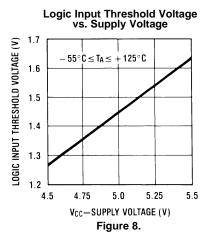

| V <sub>IN(1)</sub> , Logical "1"                    | V <sub>CC</sub> =5.25V                                       | $\overline{\text{CS}}$ , $\overline{\text{WR}}$ , $\overline{\text{RD}}$ |                    | 2.0                            |                                |                    | 2.0                                                                             | 2.0                            | V     |  |

| Input Voltage                                       | V <sub>CC</sub> =5.25V                                       | Mode                                                                     |                    | 3.5                            |                                |                    | 3.5                                                                             | 3.5                            | V     |  |

| V <sub>IN(0)</sub> , Logical "0"                    | \/ 4.75\/                                                    | CS, WR, RD                                                               |                    | 0.8                            |                                |                    | 0.8                                                                             | 0.8                            | V     |  |

| Input Voltage                                       | V <sub>CC</sub> =4.75V                                       | Mode                                                                     |                    | 1.5                            |                                |                    | 1.5                                                                             | 1.5                            | V     |  |

|                                                     | V <sub>IN(1)</sub> =5V; CS                                   | , RD                                                                     | 0.005              | 1                              |                                | 0.005              |                                                                                 | 1                              | μΑ    |  |

| I <sub>IN(1)</sub> , Logical "1"<br>Input Current   | V <sub>IN(1)</sub> =5V; ₩F                                   | ₹                                                                        | 0.1                | 3                              |                                | 0.1                | 0.3                                                                             | 3                              | μΑ    |  |

| input Gunent                                        | V <sub>IN(1)</sub> =5V; Mode                                 |                                                                          | 50                 | 200                            |                                | 50                 | 170                                                                             | 200                            | μΑ    |  |

| I <sub>IN(0)</sub> , Logical "0"<br>Input Current   | V <sub>IN(0)</sub> =0V; CS                                   | , RD, WR, Mode                                                           | -0.005             | -1                             |                                | -0.005             |                                                                                 | -1                             | μA    |  |

| V <sub>OUT(1)</sub> , Logical "1"                   | V <sub>CC</sub> =4.75V <u>, I<sub>C</sub></u><br>DB0–DB7, OI | <sub>OUT</sub> = <u>−36</u> 0 μA;<br>FL , INT                            |                    | 2.4                            |                                |                    | 2.8                                                                             | 2.4                            | >     |  |

| Output Voltage                                      | V <sub>CC</sub> =4.75V <u>, I<sub>C</sub></u><br>DB0–DB7, OI | <sub>DUT</sub> =−10 μA;<br>FL , INT                                      |                    | 4.5                            |                                |                    | 4.6                                                                             | 4.5                            | V     |  |

| V <sub>OUT(0)</sub> , Logical "0"<br>Output Voltage | V <sub>CC</sub> =4.75V <u>, I<sub>C</sub></u><br>DB0–DB7, OI | <sub>DUT</sub> = <u>1.6</u> mA;<br>FL , INT , RDY                        |                    | 0.4                            |                                |                    | 0.34                                                                            | 0.4                            | >     |  |

| I <sub>OUT</sub> , TRI-STATE                        | V <sub>OUT</sub> =5V; DB                                     | 0-DB7, RDY                                                               | 0.1                | 3                              |                                | 0.1                | 0.3                                                                             | 3                              | μΑ    |  |

| Output Current                                      | V <sub>OUT</sub> =0V; DB                                     | 0-DB7, RDY                                                               | -0.1               | -3                             |                                | -0.1               | -0.3                                                                            | -3                             | μΑ    |  |

| I <sub>SOURCE</sub> , Output                        | V <sub>OUT</sub> =0V; DB                                     | 0–DB7, OFL                                                               | -12                | -6                             |                                | -12                | -7.2                                                                            | -6                             | mA    |  |

| Source Current                                      | ĪNT                                                          |                                                                          | -9                 | -4.0                           |                                | -9                 | -5.3                                                                            | -4.0                           | mA    |  |

| I <sub>SINK</sub> , Output Sink<br>Current          | V <sub>OUT</sub> =5V; DB                                     | 0–DB7, <del>OFL</del> ,                                                  | 14                 | 7                              |                                | 14                 | 8.4                                                                             | 7                              | mA    |  |

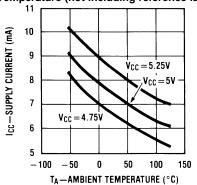

| I <sub>CC</sub> , Supply Current                    | CS =WR =RD                                                   | <del>0</del> =0                                                          | 7.5                | 15                             |                                | 7.5                | 13                                                                              | 15                             | mA    |  |

Typicals are at 25°C and represent most likely parametric norm.

Tested limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

Design limits are specified but not 100% tested. These limits are not used to calculate outgoing quality levels.

## **AC Electrical Characteristics**

The following specifications apply for  $V_{CC} = 5V$ ,  $t_r = t_f = 20$  ns,  $V_{REF}(+) = 5V$ ,  $V_{REF}(-) = 0V$  and  $T_A = 25^{\circ}C$  unless otherwise specified.

| Parameter                                                                            |                      | Conditions                                                                                           | Typ <sup>(1)</sup>    | Tested<br>Limit <sup>(2)</sup> | Design<br>Limit <sup>(3)</sup> | Units |

|--------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|--------------------------------|-------|

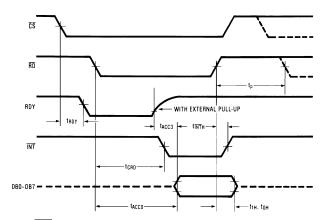

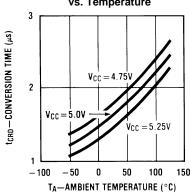

| t <sub>CRD</sub> , Conversion Time for RD Mode                                       |                      | Pin 7 = 0 (Figure 4)                                                                                 | 1.6                   |                                | 2.5                            | μs    |

| t <sub>ACC0</sub> , Access Time (Delay fr<br>Edge of RD to Output Valid)             | om Falling           | Pin 7 = 0 (Figure 4)                                                                                 | t <sub>CRD</sub> + 20 |                                | t <sub>CRD</sub> + 50          | ns    |

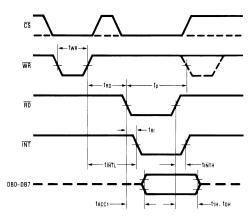

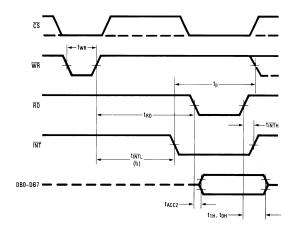

| $t_{\text{CWR-RD}}$ , Conversion Time fo Mode                                        | r WR-RD              | Pin 7 = V <sub>CC</sub> ; t <sub>WR</sub> = 600 ns, t <sub>RD</sub> =600 ns<br>(Figure 5 & Figure 6) |                       |                                | 1.52                           | μs    |

| 4 \\/.:ta T:                                                                         | Min                  | Pin 7 = V <sub>CC</sub> (Figure 5 & Figure 6)                                                        |                       | 600                            |                                | ns    |

| t <sub>WR</sub> , Write Time                                                         | Max                  | Figure 11 <sup>(4)</sup>                                                                             | 50                    |                                |                                | μs    |

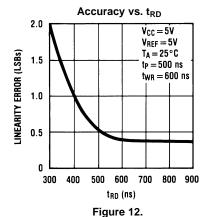

| $t_{\text{RD}}$ , Read Time                                                          | Min                  | Pin 7 = V <sub>CC</sub> (Figure 5 & Figure 6 & Figure 12) <sup>(4)</sup>                             |                       | 600                            |                                | ns    |

| t <sub>ACC1</sub> , Access Time (Delay fr                                            | om Falling           | Pin 7 = $V_{CC}$ , $t_{RD} < t_I$ , $C_L = 15pF$ (Figure 5)                                          | 190                   |                                | 280                            | ns    |

| Edge of RD to Output Valid)                                                          | · ·                  | C <sub>L</sub> = 100 pF                                                                              | 210                   |                                | 320                            | ns    |

| t <sub>ACC2</sub> , Access Time (Delay fr                                            | om Falling           | Pin 7 = $V_{CC}$ , $t_{RD} > t_I$ , $C_L = 15pF$ (Figure 6)                                          | 70                    |                                | 120                            | ns    |

| Edge of RD to Output Valid)                                                          | · ·                  | C <sub>L</sub> =100 pF                                                                               | 90                    |                                | 150                            | ns    |

| t <sub>ACC3</sub> , Access Time (Delay from Rising Edge of RDY to Output Valid)      |                      | $R_{PULLUP} = 1k$ and $C_L = 15 pF$                                                                  | 30                    |                                |                                | ns    |

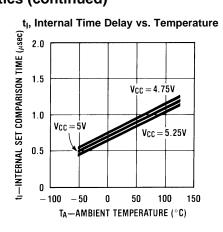

| t <sub>I</sub> , Internal Comparison Time                                            |                      | Pin 7 = V <sub>CC</sub> , C <sub>L</sub> = 50pF (Figure 6 & Figure 7)                                |                       |                                | 1300                           | ns    |

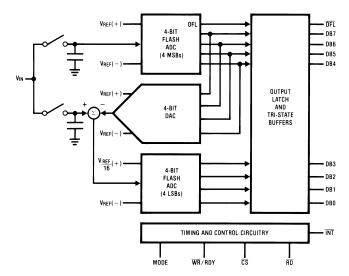

| t <sub>1H</sub> , t <sub>0H</sub> , TRI-STATE Control<br>Rising Edge of RD to Hi-Z S | (Delay from<br>tate) | R <sub>L</sub> = 1k, C <sub>L</sub> = 10 pF                                                          | 100                   |                                | 200                            | ns    |

| t <sub>INTL</sub> , Delay from Rising Edge                                           | e of WR to           | Pin 7 = $V_{CC}$ , $C_L$ = 50 pF $t_{RD}$ > $t_I$ (Figure 6)                                         |                       |                                | t <sub>l</sub>                 | ns    |

| Falling Edge of INT                                                                  |                      | t <sub>RD</sub> < t <sub>I</sub> (Figure 5)                                                          | t <sub>RD</sub> +200  |                                | t <sub>RD</sub> +290           | ns    |

| t <sub>INTH</sub> , Delay fro <u>m R</u> ising Edg<br>Rising Edge of INT             | e of RD to           | C <sub>L</sub> = 50pF (Figure 4 & Figure 5 & Figure 6)                                               | 125                   |                                | 225                            | ns    |

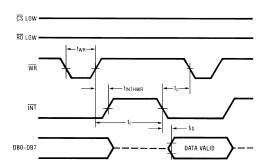

| t <sub>INTHWR</sub> , Delay <u>from</u> Rising E<br>Rising Edge of INT               | dge of WR to         | CL = 50pF (Figure 7)                                                                                 | 175                   |                                | 270                            | ns    |

| $t_{RDY}$ , Delay from $\overline{CS}$ to RDY                                        |                      | C <sub>L</sub> = 50 pF, Pin 7 = 0 (Figure 4)                                                         | 50                    |                                | 100                            | ns    |

| t <sub>ID</sub> , Delay from INT to Output                                           | Valid                | See Figure 7                                                                                         | 20                    |                                | 50                             | ns    |

| t <sub>RI</sub> , Delay from RD to INT                                               |                      | Pin 7 = V <sub>CC</sub> , t <sub>RD</sub> <t<sub>I Figure 5</t<sub>                                  | 200                   |                                | 290                            | ns    |

| t <sub>P</sub> , Delay from End of Conve<br>Conversion                               | rsion to Next        | (Figure 4 & Figure 5 & Figure 6 & Figure 7 & Figure 13) <sup>(4)</sup>                               |                       |                                | 500                            | ns    |

| Slew Rate, Tracking                                                                  |                      |                                                                                                      | 0.1                   |                                |                                | V/µs  |

| C <sub>VIN</sub> , Analog Input Capacitar                                            | nce                  |                                                                                                      | 45                    |                                |                                | pF    |

| C <sub>OUT</sub> , Logic Output Capacita                                             | nce                  |                                                                                                      | 5                     |                                |                                | pF    |

| C <sub>IN</sub> , Logic Input Capacitance                                            |                      |                                                                                                      | 5                     |                                |                                | pF    |

<sup>(2)</sup> (3) (4)

Typicals are at 25°C and represent most likely parametric norm.

Tested limits are ensured to Tl's AOQL (Average Outgoing Quality Level).

Design limits are specified but not 100% tested. These limits are not used to calculate outgoing quality levels.

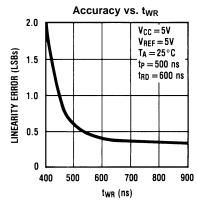

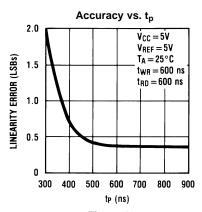

Accuracy may degrade if twR or tRD is shorter than the minimum value specified. See Figure 11 and Figure 12 graphs.

## **TRI-STATE Test Circuits and Waveforms**

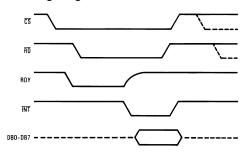

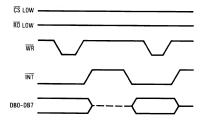

## **Timing Diagrams**

**Note:** On power-up the state of  $\overline{\mathsf{INT}}$  can be high or low.

Figure 4. RD Mode (Pin 7 is Low)

Figure 5. WR-RD Mode (Pin 7 is High and  $t_{RD} < t_I$ )

Figure 6. WR-RD Mode (Pin 7 is High and  $t_{RD}>t_I$ )

Figure 7. WR-RD Mode (Pin 7 is High) Stand-Alone Operation

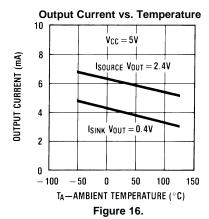

## **Typical Performance Characteristics**

Figure 10.

# Conversion Time (RD Mode) vs. Temperature

Figure 9.

Figure 11.

Figure 13.

#

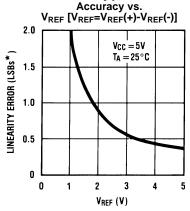

\*1 LSB= $\frac{V_{REF}}{256}$

Figure 14.

Figure 15.

#### **PIN DESCRIPTIONS**

| Pin | Name                 |                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----|----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | V <sub>IN</sub>      | Analog input; ra | nge =GND≤V <sub>IN</sub> ≤V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 2   | DB0                  | TRI-STATE data   | a output—bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 3   | DB1                  | TRI-STATE data   | RI-STATE data output—bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 4   | DB2                  | TRI-STATE data   | RI-STATE data output—bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 5   | DB3                  | TRI-STATE data   | a output—bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 6   | WR / RDY             | WR-RD Mode       | $\overline{\textbf{WR}}$ : With $\overline{\textbf{CS}}$ low, the conversion is started on the falling edge of $\overline{\textbf{WR}}$ . Approximately 800 ns (the preset internal time out, t <sub>i</sub> ) after the $\overline{\textbf{WR}}$ rising edge, the result of the conversion will be strobed into the output latch, provided that $\overline{\textbf{RD}}$ does not occur prior to this time out (See Figure 5 & Figure 6).                                                                                                                                                |  |  |  |  |

|     |                      | RD Mode          | RDY: This is an open drain output (no internal pull-up device). RDY will go low after the falling edge of $\overline{CS}$ ; RDY will go TRI-STATE when the result of the conversion is strobed into the output latch. It is used to simplify the interface to a microprocessor system (See Figure 4).                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |                      | Mode: Mode se    | lection input—it is internally tied to GND through a 50 μA current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 7   | Mode                 | RD Mode: Whe     | n mode is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     |                      | WR-RD Mode:      | When mode is high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8   | RD                   | WR-RD Mode       | With $\overline{\text{CS}}$ low, the TRI-STATE data outputs (DB0-DB7) will be activated when $\overline{\text{RD}}$ goes low (See Figure 7). $\overline{\text{RD}}$ can also be used to increase the speed of the converter by reading data prior to the preset internal time out (t <sub>I</sub> , ~800 ns). If this is done, the data result transferred to output latch is latched after the falling edge of the $\overline{\text{RD}}$ (See Figure 5 & Figure 6).                                                                                                                     |  |  |  |  |

|     |                      | RD Mode          | With $\overline{\text{CS}}$ low, the conversion will start with $\overline{\text{RD}}$ going low, also $\overline{\text{RD}}$ will enable the TRI-STATE data outputs at the completion of the conversion. RDY going TRI-STATE and $\overline{\text{INT}}$ going low indicates the completion of the conversion (See Figure 4).                                                                                                                                                                                                                                                            |  |  |  |  |

| 9   | ĪNT                  | WR-RD Mode       | $\overline{\text{INT}}$ going low indicates that the conversion is completed and the data result is in the output latch. $\overline{\text{INT}}$ will go low, ~800 ns (the preset internal time out, $t_i$ ) after the rising edge of $\overline{\text{WR}}$ (See Figure 6); or $\overline{\text{INT}}$ will go low after the falling edge of $\overline{\text{RD}}$ , if $\overline{\text{RD}}$ goes low prior to the 800 ns time out (See Figure 5). $\overline{\text{INT}}$ is reset by the rising edge of $\overline{\text{RD}}$ or $\overline{\text{CS}}$ (See Figure 5 & Figure 6). |  |  |  |  |

|     |                      | RD Mode          | INT going low indicates that the conversion is completed and the data result is in the output latch. INT is reset by the rising edge of RD or CS (See Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 10  | GND                  | Ground           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 11  | V <sub>REF</sub> (-) | The bottom of re | esistor ladder, voltage range: GND≤V <sub>REF</sub> (−)≤V <sub>REF</sub> (+) <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 12  | V <sub>REF</sub> (+) | The top of resis | tor ladder, voltage range: V <sub>REF</sub> (−)≤V <sub>REF</sub> (+)≤V <sub>CC</sub> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 13  | <del>CS</del>        | CS must be low   | in order for the $\overline{RD}$ or $\overline{WR}$ to be recognized by the converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 14  | DB4                  | TRI-STATE data   | a output—bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 15  | DB5                  | TRI-STATE data   | a output—bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 16  | DB6                  | TRI-STATE data   | a output—bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 17  | DB7                  | TRI-STATE data   | a output—bit 7 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 18  | OFL                  | be used to case  | —If the analog input is higher than the $V_{REF}(+)$ , $\overline{OFL}$ will be low at the end of conversion. It can ade 2 or more devices to have more resolution (9, 10-bit). This output is always active and does STATE as DB0–DB7 do.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 19  | NC                   | No connection    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 20  | V <sub>CC</sub>      | Power supply vo  | oltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

<sup>(1)</sup> When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supply rails (V<sub>IN</sub> < V<sup>-</sup>or V<sub>IN</sub> > V<sup>+</sup>) the absolute value of current at that pin should be limited to 1 mA or less. The 4 mA package input current limits the number of pins that can exceed the power supply boundaries with a 1 mA current limit to four.

#### **FUNCTIONAL DESCRIPTION**

#### **GENERAL OPERATION**

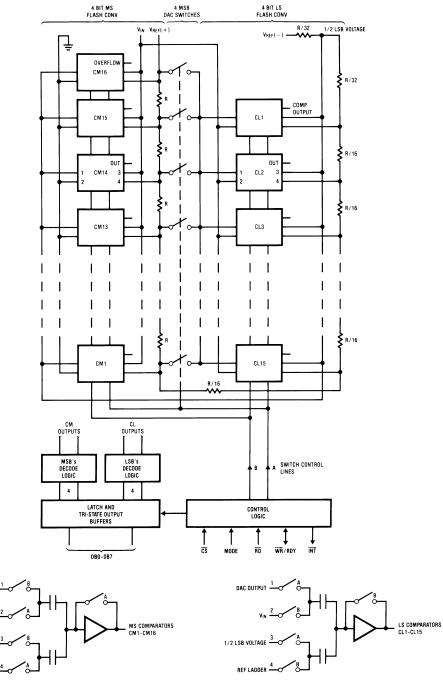

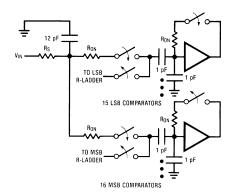

The ADC0820-N uses two 4-bit flash A/D converters to make an 8-bit measurement (Figure 3). Each flash ADC is made up of 15 comparators which compare the unknown input to a reference ladder to get a 4-bit result. To take a full 8-bit reading, one flash conversion is done to provide the 4 most significant data bits (via the MS flash ADC). Driven by the 4 MSBs, an internal DAC recreates an analog approximation of the input voltage. This analog signal is then subtracted from the input, and the difference voltage is converted by a second 4-bit flash ADC (the LS ADC), providing the 4 least significant bits of the output data word.

The internal DAC is actually a subsection of the MS flash converter. This is accomplished by using the same resistor ladder for the A/D as well as for generating the DAC signal. The DAC output is actually the tap on the resistor ladder which most closely approximates the analog input. In addition, the "sampled-data" comparators used in the ADC0820-N provide the ability to compare the magnitudes of several analog signals simultaneously, without using input summing amplifiers. This is especially useful in the LS flash ADC, where the signal to be converted is an analog difference.

#### THE SAMPLED-DATA COMPARATOR

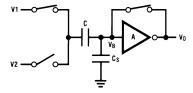

Each comparator in the ADC0820-N consists of a CMOS inverter with a capacitively coupled input (Figure 17 Figure 18). Analog switches connect the two comparator inputs to the input capacitor (C) and also connect the inverter's input and output. This device in effect now has one differential input pair. A comparison requires two cycles, one for zeroing the comparator, and another for making the comparison.

In the first cycle, one input switch and the inverter's feedback switch (Figure 17) are closed. In this interval, C is charged to the connected input (V1) less the inverter's bias voltage ( $V_B$ , approximately 1.2V). In the second cycle (Figure 18), these two switches are opened and the other (V2) input's switch is closed. The input capacitor now subtracts its stored voltage from the second input and the difference is amplified by the inverter's open loop gain. The inverter's input ( $V_B$ ) becomes

$$V_{B} - (V1 - V2) \frac{C}{C + C_{S}}$$

(1)

and the output will go high or low depending on the sign of V<sub>B</sub>'-V<sub>B</sub>.

The actual circuitry used in the ADC0820-N is a simple but important expansion of the basic comparator described above. By adding a second capacitor and another set of switches to the input (Figure 19), the scheme can be expanded to make dual differential comparisons. In this circuit, the feedback switch and one input switch on each capacitor (Z switches) are closed in the zeroing cycle. A comparison is then made by connecting the second input on each capacitor and opening all of the other switches (S switches). The change in voltage at the inverter's input, as a result of the change in charge on each input capacitor, will now depend on both input signal differences.

- $V_O = V_B$

- V on C =  $V1-V_B$

- C<sub>S</sub> = stray input node capacitor

- V<sub>B</sub> = inverter input bias voltage

Zeroing Phase

Figure 17. Sampled-Data Comparator

Compare Phase

$$\begin{aligned} \bullet V_B' - V_B &= (V2 - V1) \frac{C}{C + C_S} \\ \bullet V_O' &= \frac{-A}{C + C_S} \left[ CV2 - CV1 \right] \\ \bullet V_O' &= \frac{-A}{C + C_S} \left[ CV2 - CV1 \right] \\ \bullet V_O' &= \frac{-A}{C + C_S} \left[ \Delta Q_{C1} + \Delta Q_{C2} \right] \end{aligned}$$

Figure 18. Sampled-Data Comparator

Figure 19. ADC0820-N Comparator (from MS Flash ADC)

#### **ARCHITECTURE**

In the ADC0820-N, one bank of 15 comparators is used in each 4-bit flash A/D converter (Figure 25). The MS (most significant) flash ADC also has one additional comparator to detect input overrange. These two sets of comparators operate alternately, with one group in its zeroing cycle while the other is comparing.

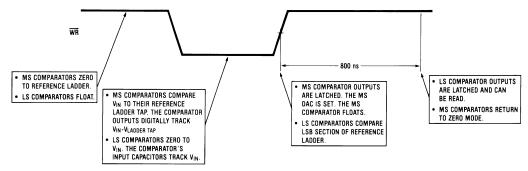

When a typical conversion is started, the  $\overline{\text{WR}}$  line is brought low. At this instant the MS comparators go from zeroing to comparison mode (Figure 24). When  $\overline{\text{WR}}$  is returned high after at least 600 ns, the output from the first set of comparators (the first flash) is decoded and latched. At this point the two 4-bit converters change modes and the LS (least significant) flash ADC enters its compare cycle. No less than 600 ns later, the  $\overline{\text{RD}}$  line may be pulled low to latch the lower 4 data bits and finish the 8-bit conversion. When  $\overline{\text{RD}}$  goes low, the flash A/Ds change state once again in preparation for the next conversion.

Figure 24 also outlines how the converter's interface timing relates to its analog input  $(V_{IN})$ . In WR-RD mode,  $V_{IN}$  is measured while  $\overline{WR}$  is low. In RD mode, sampling occurs during the first 800 ns of RD. Because of the input connections to the ADC0820-N's LS and MS comparators, the converter has the ability to sample  $V_{IN}$  at one instant (see Inherent Sample-Hold), despite the fact that two separate 4-bit conversions are being done. More specifically, when  $\overline{WR}$  is low the MS flash is in compare mode (connected to  $V_{IN}$ ), and the LS flash is in zero mode (also connected to  $V_{IN}$ ). Therefore both flash ADCs sample  $V_{IN}$  at the same time.

#### **DIGITAL INTERFACE**

The ADC0820-N has two basic interface modes which are selected by strapping the MODE pin high or low.

#### **RD Mode**

With the MODE <u>pin</u> grounded, the converter is set to Re<u>ad mode</u>. In this configuration, a complete conversion is done by pulling RD low until output data appears. An <u>INT</u> line is provided which goes low at the end of the conversion as well as a RDY output which can be used to signal a processor that the converter is busy or can also serve as a system Transfer Acknowledge signal.

Figure 20. RD Mode (Pin 7 is Low)

When in RD mode, the comparator phases are internally triggered. At the falling edge of  $\overline{RD}$ , the MS flash converter goes from zero to compare mode and the LS ADC's comparators enter their zero cycle. After 800 ns, data from the MS flash is latched and the LS flash ADC enters compare mode. Following another 800 ns, the lower 4 bits are recovered.

#### WR then RD Mode

With the MODE pin tied high, the A/D will be set up for the WR-RD mode. Here, a conversion is started with the WR input; however, there are two options for reading the output data which relate to interface timing. If an interrupt driven scheme is desired, the user can wait for INT to go low before reading the conversion result (Figure 22). INT will typically go low 800 ns after WR's rising edge. However, if a shorter conversion time is desired, the processor need not wait for INT and can exercise a read after only 600 ns (Figure 21). If this is done, INT will immediately go low and data will appear at the outputs.

Figure 21. WR-RD Mode (Pin 7 is High and t<sub>RD</sub><t<sub>I</sub>)

Figure 22. WR-RD Mode (Pin 7 is High and t<sub>RD</sub>>t<sub>I</sub>)

#### Stand-Alone

<u>For</u> stand-alone operation in WR-RD mode,  $\overline{CS}$  and  $\overline{RD}$  can be tied low and a conversion can be started with WR. Data will be valid approximately 800 ns following WR's rising edge.

Figure 23. WR-RD Mode (Pin 7 is High) Stand-Alone Operation

**Note:** MS means most significant LS means least significant

Figure 24. Operating Sequence (WR-RD Mode)

## OTHER INTERFACE CONSIDERATIONS

In order to maintain conversion accuracy,  $\overline{WR}$  has a maximum width spec of 50 µs. When the MS flash ADC's sampled-data comparators (see The Sampled-Data Comparator) are in comparison mode (WR is low), the input capacitors (C, Figure 19) must hold their charge. Switch leakage and inverter bias current can cause errors if the comparator is left in this phase for too long.

Copyright © 1999–2013, Texas Instruments Incorporated Submit Docum

Since the MS flash ADC enters its zeroing phase at the end of a conversion (see Architecture), a new conversion cannot be started until this phase is complete. The minimum spec for this time (t<sub>P</sub>, see Figure 4 & Figure 5 & Figure 6 & Figure 7) is 500 ns.

## **Detailed Block Diagram**

Figure 25.

#### **Analog Considerations**

#### REFERENCE AND INPUT

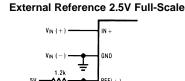

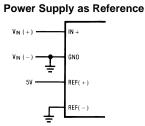

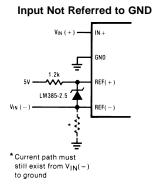

The two  $V_{REF}$  inputs of the ADC0820-N are fully differential and define the zero to full-scale input range of the A to D converter. This allows the designer to easily vary the span of the analog input since this range will be equivalent to the voltage difference between  $V_{IN}(+)$  and  $V_{IN}(-)$ . By reducing  $V_{REF}(V_{REF} = V_{REF}(+) - V_{REF}(-))$  to less than 5V, the sensitivity of the converter can be increased (i.e., if  $V_{REF} = 2V$  then 1 LSB = 7.8 mV). The input/reference arrangement also facilitates ratiometric operation and in many cases the chip power supply can be used for transducer power as well as the  $V_{REF}$  source.

This reference flexibility lets the input span not only be varied but also offset from zero. The voltage at  $V_{REF}(-)$  sets the input level which produces a digital output of all zeroes. Though  $V_{IN}$  is not itself differential, the reference design affords nearly differential-input capability for most measurement applications. Figure 26 shows some of the configurations that are possible.

#### INPUT CURRENT

Due to the unique conversion techniques employed by the ADC0820-N, the analog input behaves somewhat differently than in conventional devices. The A/D's sampled-data comparators take varying amounts of input current depending on which cycle the conversion is in.

The equivalent input circuit of the ADC0820-N is shown in Figure 27. When a conversion starts ( $\overline{\text{WR}}$  low, WR-RD mode), all input switches close, connecting  $V_{\text{IN}}$  to thirty-one 1 pF capacitors. Although the two 4-bit flash circuits are not both in their compare cycle at the same time,  $V_{\text{IN}}$  still sees all input capacitors at once. This is because the MS flash converter is connected to the input during its compare interval and the LS flash is connected to the input during its zero-phase (see Architecture). In other words, the LS ADC uses  $V_{\text{IN}}$  as its zero-phase input.

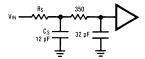

The input capacitors must charge to the input voltage through the on resistance of the analog switches (about 5 k $\Omega$  to 10 k $\Omega$ ). In addition, about 12 pF of input stray capacitance must also be charged. For large source resistances, the analog input can be modeled as an RC network as shown in Figure 28. As R<sub>S</sub> increases, it will take longer for the input capacitance to charge.

In RD mode, the input switches are closed for approximately 800 ns at the start of the conversion. In WR-RD mode, the time that the switches are closed to allow this charging is the time that  $\overline{WR}$  is low. Since other factors force this time to be at least 600 ns, input time constants of 100 ns can be accommodated without special consideration. Typical total input capacitance values of 45 pF allow  $R_S$  to be 1.5 k $\Omega$  without lengthening  $\overline{WR}$  to give  $V_{IN}$  more time to settle.

LM385-2.5

Figure 26. Analog Input Options

Figure 27. ADC0820-N Input Circuit

Figure 28. Analog Input, RC Network Model

#### **INPUT FILTERING**

It should be made clear that transients in the analog input signal, caused by charging current flowing into  $V_{IN}$ , will not degrade the A/D's performance in most cases. In effect the ADC0820-n does not "look" at the input when these transients occur. The comparators' outputs are not latched while  $\overline{WR}$  is low, so at least 600 ns will be provided to charge the ADC's input capacitance. It is therefore not necessary to filter out these transients by putting an external cap on the  $V_{IN}$  terminal.

#### **INHERENT SAMPLE-HOLD**

Another benefit of the ADC0820-N's input mechanism is its ability to measure a variety of high speed signals without the help of an external sample-and-hold. In a conventional SAR type converter, regardless of its speed, the input must remain at least ½ LSB stable throughout the conversion process if full accuracy is to be maintained. Consequently, for many high speed signals, this signal must be externally sampled, and held stationary during the conversion.

Sampled-data comparators, by nature of their input switching, already accomplish this function to a large degree (see The Sampled Data Comparator). Although the conversion time for the ADC0820-N is 1.5  $\mu$ s, the time through which  $V_{IN}$  must be ½ LSB stable is much smaller. Since the MS flash ADC uses  $V_{IN}$  as its "compare" input and the LS ADC uses  $V_{IN}$  as its "zero" input, the ADC0820-N only "samples"  $V_{IN}$  when  $\overline{WR}$  is low (see Architecture and Input Current). Even though the two flashes are not done simultaneously, the analog signal is measured at one instant. The value of  $V_{IN}$  approximately 100 ns after the rising edge of  $\overline{WR}$  (100 ns due to internal logic prop delay) will be the measured value.

Input signals with slew rates typically below 100 mV/ $\mu$ s can be converted without error. However, because of the input time constants, and charge injection through the opened comparator input switches, faster signals may cause errors. Still, the ADC0820-N's loss in accuracy for a given increase in signal slope is far less than what would be witnessed in a conventional successive approximation device. An SAR type converter with a conversion time as fast as 1  $\mu$ s would still not be able to measure a 5V 1 kHz sine wave without the aid of an external sample-and-hold. The ADC0820-N, with no such help, can typically measure 5V, 7 kHz waveforms.

## **Typical Applications**

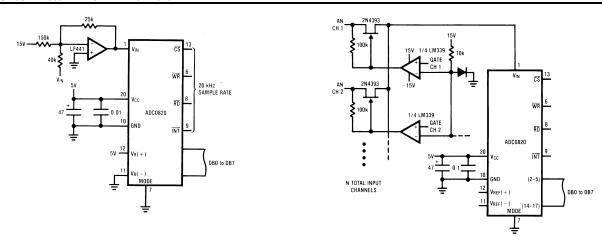

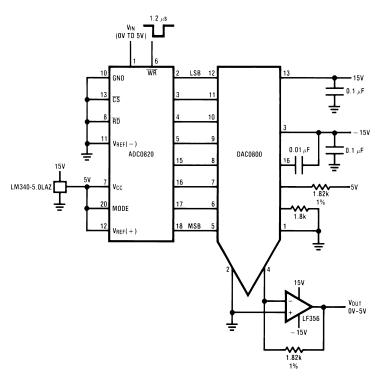

Figure 29. 8-Bit Resolution Configuration

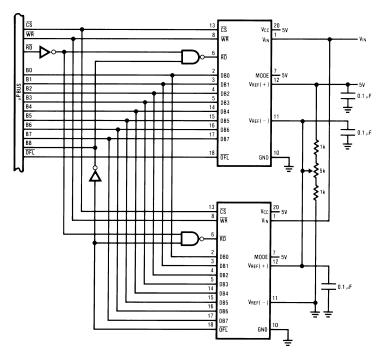

Figure 30. 9-Bit Resolution Configuration

- $V_{IN}=3 \text{ kHz max} \pm 4V_P$

- No track-and-hold needed

- Low power consumption

Figure 31. Telecom A/D Converter

Figure 32. Multiple Input Channels

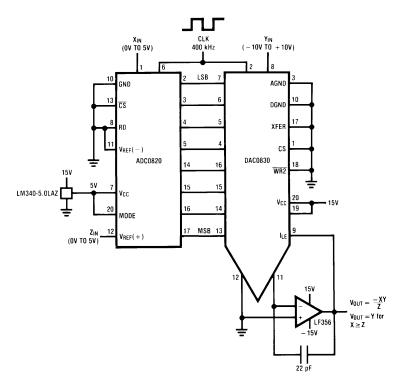

Figure 33. 8-Bit 2-Quadrant Analog Multiplier

Figure 34. Fast Infinite Sample-and-Hold

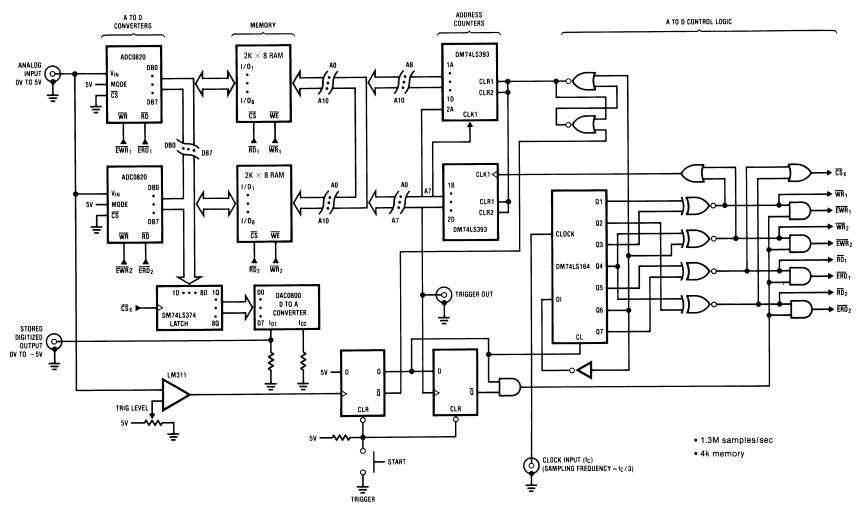

Figure 35. Digital Waveform Recorder

## **REVISION HISTORY**

| Cł | hanges from Revision B (March 2013) to Revision C  | Pa | ge |

|----|----------------------------------------------------|----|----|

| •  | Changed layout of National Data Sheet to TI format |    | 20 |

12-Jul-2014

#### **PACKAGING INFORMATION**

| Orderable Device  | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|-------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| ADC0820BCWMX/NOPB | ACTIVE | SOIC         | DW                 | 20   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | ADC0820<br>BCWM      | Samples |

| ADC0820CCN/NOPB   | ACTIVE | PDIP         | NFH                | 20   | 18             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-NA-UNLIM    | -40 to 85    | ADC0820CCN           | Samples |

| ADC0820CCN/PB     | NRND   | PDIP         | NFH                | 20   | 18             | TBD                        | Call TI          | Call TI             |              | ADC0820CCN           |         |

| ADC0820CCWM       | NRND   | SOIC         | DW                 | 20   | 36             | TBD                        | Call TI          | Call TI             | -40 to 85    | ADC0820<br>CCWM      |         |

| ADC0820CCWM/NOPB  | ACTIVE | SOIC         | DW                 | 20   | 36             | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | ADC0820<br>CCWM      | Samples |

| ADC0820CCWMX/NOPB | ACTIVE | SOIC         | DW                 | 20   | 1000           | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | ADC0820<br>CCWM      | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

## **PACKAGE OPTION ADDENDUM**

12-Jul-2014

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 23-Sep-2013

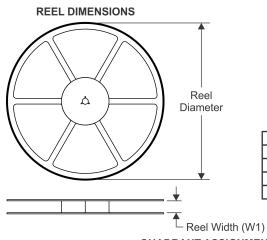

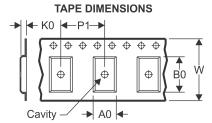

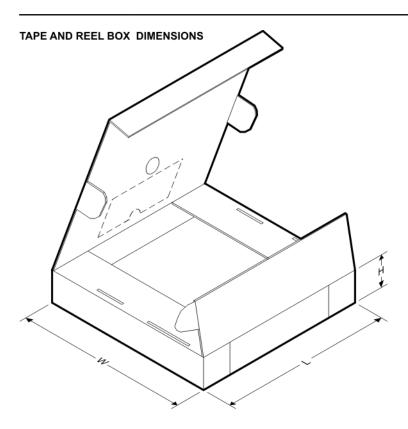

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

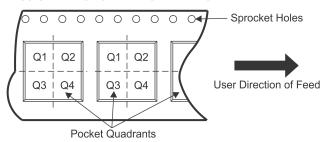

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADC0820BCWMX/NOPB | SOIC            | DW                 | 20 | 1000 | 330.0                    | 24.4                     | 10.9       | 13.3       | 3.25       | 12.0       | 24.0      | Q1               |

| ADC0820CCWMX/NOPB | SOIC            | DW                 | 20 | 1000 | 330.0                    | 24.4                     | 10.9       | 13.3       | 3.25       | 12.0       | 24.0      | Q1               |

www.ti.com 23-Sep-2013

#### \*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADC0820BCWMX/NOPB | SOIC         | DW              | 20   | 1000 | 367.0       | 367.0      | 45.0        |

| ADC0820CCWMX/NOPB | SOIC         | DW              | 20   | 1000 | 367.0       | 367.0      | 45.0        |

DW (R-PDSO-G20)

## PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AC.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom Amplifiers amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>